## CALCOLATORI ELETTRONICI A – 30 agosto 2010

| NOME:                                       | COGNOME: | <b>MATR:</b> |

|---------------------------------------------|----------|--------------|

| Scrivere chiaramente in caratteri majuscoli | a stampa |              |

1. Si implementi per mezzo di porte logiche di AND, OR e NOT la funzione combinatoria (a 4 ingressi e una uscita) che riceve in ingresso due valori positivi binari  $\overline{x}$  e  $\overline{y}$  ciascuno di 2 bit  $(\overline{x} = x_1x_0 \text{ e } \overline{y} = y_1y_0)$  e pone in uscita  $1 \text{ se } \overline{x} \ge \overline{y}$ , pone in uscita 0 altrimenti. Si esprima inoltre la dimensione dell'implementazione per mezzo di PLA e la dimensione dell'implementazione per mezzo di memoria ROM. [5]

2. Utilizzando la green card, tradurre in linguaggio macchina le seguenti due istruzioni espresse in assembly MIPS: [4]

L1: addi \$t0, \$t0, -1

bne \$t0, \$zero, L1

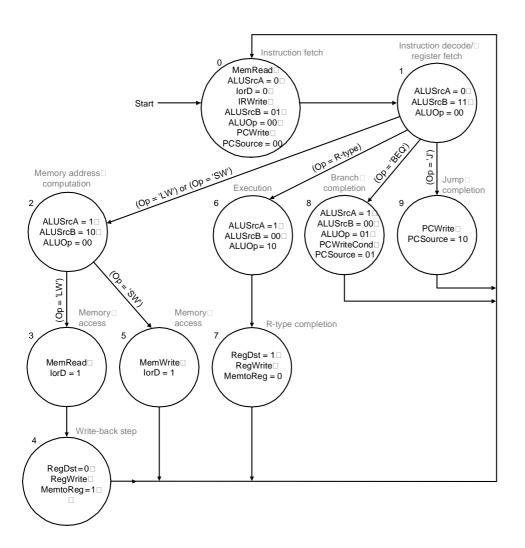

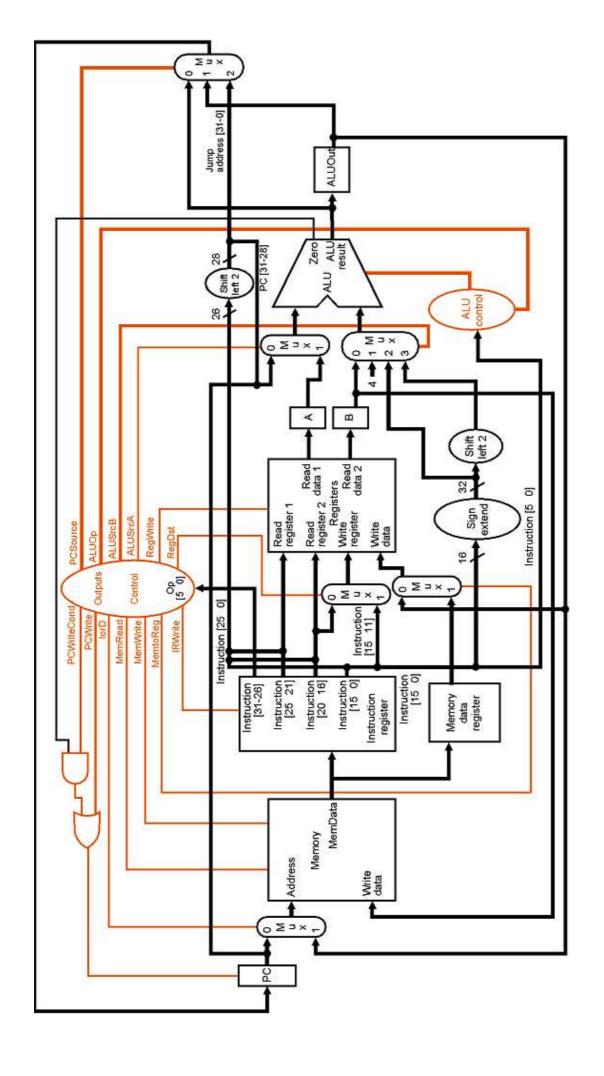

3. Si considerino, mostrati nelle figure alla pagina seguente, il datapath ed il diagramma a stati finiti che specifica l'unità di controllo secondo la tecnica a multiciclo relativamente alle istruzioni MIPS *lw*, *sw*, *beq*, *j* ed alle istruzioni *Tipo-R*. Si vuole implementare la nuova istruzione

che, a partire dall'indirizzo r2 e procedendo verso indirizzi decrescenti, ricerca in memoria la prima occorrenza del valore (a 32 bit) specificato in r1. L'istruzione deve ricercare il valore fino all'indirizzo 4 (ovvero, escludendo l'indirizzo  $\theta$ ): se il valore viene trovato, il rispettivo indirizzo viene posto in r0, se il valore non viene trovato l'istruzione pone in r0 il valore  $\theta$ .

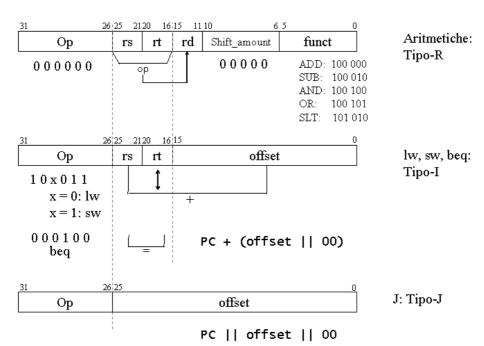

Ricordando i tre formati di codifica delle istruzioni (riportati di seguito) si chiede di:

- riportare il formato della nuova istruzione macchina (specificando anche i campi destinati a r1 e r2);

- riportare, nella corrispondente figura, le modifiche necessarie al datapath;

- estendere il diagramma degli stati per implementare la nuova istruzione. [10]

## Promemoria formati delle istruzioni:

4. Si consideri la nota implementazione dell'unità di controllo secondo la tecnica multiciclo relativamente alle istruzioni MIPS lw, sw, beq, j e TIPO-R (cfr. esercizio precedente). Si supponga che le operazioni atomiche che coinvolgono le unità funzionali principali richiedano:

Unità di memoria (lettura e scrittura): 2 ns Register File (lettura e scrittura): 1 ns Operazione ALU: 2 ns

Si ipotizzi che il carico di lavoro preveda in ogni caso, per le istruzioni sw e TIPO-R, una percentuale complessiva del 50%:

$$f_{SW} + f_{TIPO-R} = 50\%$$

Si chiede, riportando i passi significativi dell'analisi, di:

- a) Determinare le condizioni in cui un'implementazione a singolo ciclo risulta più conveniente, in termini di prestazioni, rispetto all'implementazione multiciclo.

- b) Rispondere alla stessa domanda supponendo che la lettura e la scrittura del Register File richiedano 2 ns al posto di 1 ns. [4]

5. Scrivere una procedura in assembler MIPS corrispondente alla seguente funzione ricorsiva espressa in linguaggio C. Si utilizzino le note convenzioni sui registri. [6]

```

int F(int a, int b){

if(b>a || a<=100) return a+b;

else return F(b-a, 3b);

}</pre>

```